▣ CPU_파이프라인, 슈퍼 파이프라인, 슈퍼 스칼라, 슈퍼 파이프라인 슈퍼 스칼라, VLIW(Very long Instruction World), EPIC, 해저드

CPU 처리성능 향상을 위해 Instruction 처리 과정을 여러 단계로 세분화하는 병렬처리 기법

- Instruction Fetch (IF) : 다음에 실행할 명령어를 명령어 레지스터 저장

- Instruction Decode (ID) : 명령어를 해석

- Execution (EX) : 해석한 결과로 명령어 실행

- Write Back (WB) : 실행결과 메모리에 저장

– T: 명령어 실행 시간, k: 파이프라인 단계, N 실행 명령어 수

| 구분 | 개념도 | 내용 |

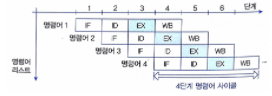

| 파이프라인 | 순차적인 병렬처리가 아닌 상호 충돌하지 않은 명령어 처리 단계를 병렬로 처리하여 다중 명령의 실행을 효과적으로 수행하고 성능을 향상시키는 병렬처리 기법 (명령어의 실행 Overlapping으로 구현) - Micro Instruction 기반 병렬처리 - Pt = k + (N – 1) |

|

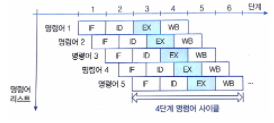

| 슈퍼 파이프라인 | 하나의 Pipeline을 여러부분으로 나누어 연속적인 흐름과정을 처리함으로써 성능을 향상하는 병렬처리 기술 Pipeline Stage를 세분화하여 Clock Cycle시간을 줄여 속도향상 - CPU Clock Degree 기반 파이프라인 - SPt = k + 1/n * (N – 1) n: CPU Clock degree (1 Clock 당 수행 횟수) |

|

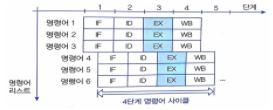

| 슈퍼 스칼라 | 프로세서 내에 Pipeline된 ALU를 여러개 포함시켜서 매 사이클마다 복수의 명령어들이 동시에 실행될 수 있도록 하는 병렬 처리 기술 - 다수 기능 유닛기반 파이프라인 중첩 - SSt = k + (N – m)/m m: 파이프라인 중첩 수 |

|

| 슈퍼 파이프라인 슈퍼 스칼라 |

- CPU Clock Degree기반 파이프라인 중첩 - SPSSt = k + (N – m)/(m * n) |

|

| VLIW (Explicitly Parallel Instruction Computing) |

동시에 수행될 수 있는 명령어들을 컴파일러 수준에서 추출하여 하나의 명령어로 압축하여 수행하는 병렬처리 기술(컴파일시 검출) - 동시 수행 명령어를 컴파일러 수준으로 추출 - Instruction 압축 |

|

| EPIC | - 컴파일러가 병렬성을 찾아내는 아키텍처 - HP와 Intel 공동개발 Intel Itanium (IA64) - 사용자의 컴파일러가 소스 코드로부터 병렬성을 찾아내고 병렬처리용 기계어 코드를 생성하여 수행하는 방식 |

|

암기 슈파분슈스병

* 출처 : 도리의 디지털라이프

– 파이프라인 기반 명령어 처리 시 병렬처리 특성으로 인한 구조적, 데이터, 제어 해저드에 따른 대응 필요

| 종류 | 세부 설명 | 해소방안 |

| 구조적 해저드 (Structural Hazards) |

파이프라인의 두 명령어가 동시에 한 하드웨어에 접근할 때 발생 같은 메모리 접근 등 하드웨어가 병행 수행을 지원하지 않는 경우 자원 충돌(Resource Conflicts) 발생 |

명령어 메모리와 데이터 메모리 분리 |

| 데이터 해저드 (Data Hazards) |

현재 파이프라인에서 수행중인 명령에서 사용하는 데이터가 다음 파이프라인에서도 사용될 경우 다음 파이프라인은 현재 파이프라인이 해당 데이터를 모두 사용할 때까지 기다려야 함 명령 값이 이전 명령에 종속되어 대기함 |

Forwarding, 컴파일러의 명령어 스케쥴링 |

| 제어 해저드 (Control Hazards) |

분기가 발생하면 다음 파이프라인은 모두 의미가 없어짐 분기(jump, branch 등) 명령어에 의해 처리 |

분기 예측, 지연 분기(명령어 실행순서를 재배치) |

2017년 86번

정답 : 3번

1) k-단계 명령어 파이프라인을 사용하면 k배를 초과하는 속도 향상을 얻을 수 있다.

-> k 단계를 나누어도 k배 만큼의 속도 향상을 얻을 수는 없음.

파이프라인 해저드 등 병렬처리를 방해하는 요소들이 많기 때문임

2) 파이프라인 클록은 처리시간이 가장 짧은 단계를 기준으로 정해진다.

-> 가장 긴 단계를 기준으로 정해야 함

3) 수퍼파이프라이닝(superpipelining) 기술은 단계들을 더욱 작게 분할하는 기술이다. (맞음)

4) 구조 해저드(structural hazard)문제를 해결하기 위해 지연 분기(delayed branch) 또는 루프 버퍼 기법을 사용한다.

-> 제어 해저드 방식임

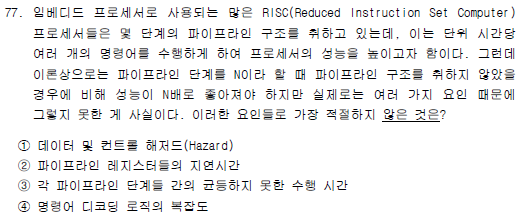

2011년 77번

정답 : 4번

명령어 디코딩 로직의 복잡도는 파이프라인 속도 저하와 상관 없음

명령어 디코딩 로직은 하나의 파이프라인이 아니라 모든 파이프라인이 공통적으로 걸려 있는 것이기 때문에 파이프라인 간의 속도 저하와는 상관 없음

'시스템구조' 카테고리의 다른 글

| 행정공공기관 영상회의시스템 상호연계 기술 표준 규격 (0) | 2021.10.22 |

|---|---|

| 정보시스템 백업 지침_전체백업, 증분백업, 차등 백업, 합성 백업, 중복제거 백업 (0) | 2021.10.22 |

| RFID_액티브(Active) 방식, 패시브(Passive) 방식, EPC, 미들웨어 Savant, PML (0) | 2021.10.21 |

| 사물인터넷 참조모델_응용 계층, 서비스 지원 및 응용 지원 계층, 네트워크 계층, 디바이스 계층, 관리기능, 보안기능 (0) | 2021.10.21 |

| 센서_자이로, 방향, 가속도, 이미지 (0) | 2021.10.21 |